|

D0 (DZero)

Считывающая электроника

для передней мюонной трековой системы

установки D0 (DZero), FNAL, USA.

|

|

|

|

|

9U VME FE крейты

|

MDRC-контроллер крейта

|

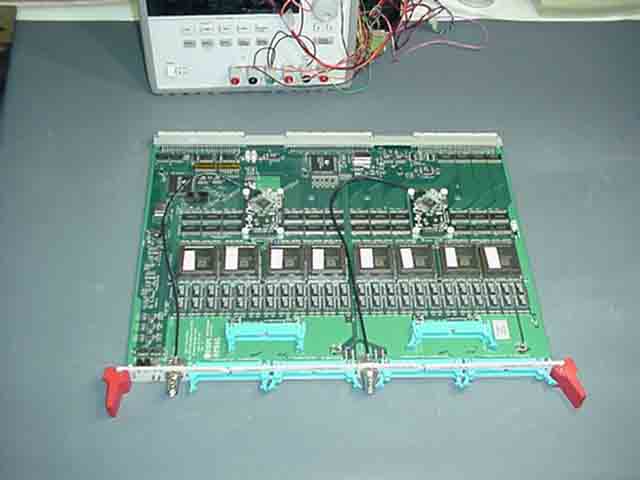

MDC плата

|

-

Считывающая электроника предназначена для работы в составе передней мюонной трековой

системы установки D0, FNAL, USA.

D0 является одним из двух коллайдерных детекторов Теватрона (D0, CDF). Столкновения частиц происходят каждые 132 нс, с тремя зазорами. Информация считывается с детектора, выполненного на

основе MDT (Mini Drift Tubes). Электроника MDT FE спроектирована с учетом требований, выработанных на D0:

- отсутствие мертвого времени при регистрации данных; входные данные непрерывно регистрируются, отсылаются на Триггер Первого Уровня (L1 Trigger) и временно запоминаются до получения решения от Триггера Первого Уровня;

- после получения решения Триггера Первого Уровня (L1 Accept) требуемые данные помещаются в Буфер Первого Уровня (L1 FIFO) для последующего считывания, обработки и передачи на Триггер Второго Уровня (L2 Trigger) и при необходимости Третьего Уровня (L3 Trigger);

- форматирование данных, формирование буферов и другие служебные функции осуществляются с помощью быстродействующих процессоров (ADSP, Analog Devices);

- процесс регистрации данных строго синхронизирован с моментами столкновения частиц в центре установки. Специальные меры приняты для поддержания и контроля синхронности работы системы;

- в системе предусмотрен ряд цифровых управляемых задержек, позволяющих учесть кабельные задержки, задержку решения Триггера Первого Уровня и т.п. и обеспечить синхронную работу системы с Глобальной Системой Считывания Установки D0

- считанные данные передаются по скоростным последовательным коаксиальным каналам связи (L1 Data - 1 Gbit/sec, L2-L3 Data - 160 Mbit/sec);

- в системе предусмотрены возможности для автономной работы и развитые средства тестирования и самоконтроля.

Системой обслуживается около 50000 MDT каналов. При этом, кроме регистрации

факта срабатывания каждого из каналов, грубо оценивается время дрейфа (18,83 ns/bin),

позволяющее улучшить пространственное разрешение трубок. Считывающая электроника

располагается в 24-x 9U VME FE крейтах, установленных непосредственно на

платформе детектора D0 (Collision Hall). В каждом из этих VME крейтов установлен

VME master (VSB-20), контроллер крейта MDRC и 10-12 MDC, непосредственно

соединенных с предусилителями MDT. VME FE крейты отличаются друг от друга

лишь числом обслуживаемых каналов, адресами и набором загружаемых параметров.

Каждый MDC обслуживает 192 канала.

MDRC обеспечивает необходимую синхронизацию в пределах крейта, скоростное

считывание MDCs по спецмагистрали, (J3) форматирование, передачу данных и некоторые другие служебные функции.

@ D0 Muon Electronics Homepage

@ MDT electronics

@ MDC Specification

@ MDRC Specification

@ MDT software

|

D0 English page

|