Устройство поиска треков (Track Finder) реализуется как 12 процессоров, каждый из которых идентифицирует до трех лучших мюонов в 60-градусном азимутальном секторе.

Алгоритм поиска треков использует трехмерное измерение траекторий для достижения максимальной эффективности в подавлении фона. Целью процессора поиска треков является анализ входных

примитивных треков (трековых сегментов) от индивидуальных катодных стриповых станций для построения полных треков, измерение поперечного импульса

p t, индуцированного

изгибающим магнитным моментом, и передача глобальному триггеру первого уровня соообщения о количестве и качестве полных треков.

Блок-схема Процессора поиска треков показана на рис.1. Вход процессора способен анализировать трековые сегменты от нескольких дискретных временных

интервалов (bunch crossing - BX). Схема анализа временных интервалов (BXA) накапливает трековые сегменты от нескольких временных интервалов и корректирует ошибки, если трековые сегменты одного события находятся в соседних временных интервалах.

Схемы экстраполяции (EU) берут информацию от двух трековых сегментов в разных катодных стриповых станциях и проверяют их на совпадение с номинальным изгибом траектории в данном регионе.

Схемы ассемблера треков (TAU) анализируют выходы схем экстраполяции и определяют трековые пары, относящиеся к одному и тому же мюону.

Схема окончательного отбора (FSU) собирает информацию от схем ассемблеров треков, исключает избыточные треки и выбирает три лучших трека. Схема ассигнования (AU) измеряет поперечный импульс на финальной стадии обработки данного события.

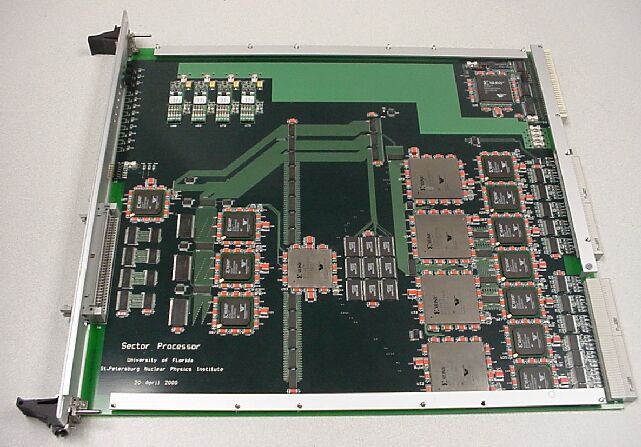

Первый прототип процессора (Рис.2) был разработан в 2000 году и успешно испытан в 2000-2001 годах. Это 9U VME модуль глубиной 400 мм. На плате расположены 17 микросхем с программируемыми связями (FPGA)

фирмы Xilinx. Окончательный, сигнальный прототип процессора в настоящее время находится в стадии разработки. Новый процессор занимает только одну сверхбольшую (выпуска 2002 года) микросхему FPGA. Это позволило разместить на одной плате и три приемника информации от катодных

стриповых камер, что сократило число плат всего устройства поиска треков по сравнению с первым прототипом в четыре раза. Это также позволило сократить время решения процессора с 375 нсек до 175 нсек. Соласно расписанию трассировка платы процессора должна быть закончена в сентябре

2002 года. Производство процессора должно закончиться в ноябре 2002 года, а отладка и тестирование - в апреле 2003 года.

* - в настоящее время сотрудник фирмы Солидум, Канада.

[1] - CMS The TriDas Project Technical Design Report, Volume 1:

The Trigger Systems p.217-248